Learn about Kobe University and their research into the design and evaluation of semiconductor IC chips and VLSI systems for better safety and security.

The graduate school of Science, Technology and Innovation at Kobe University are currently looking at the design and evaluation of semiconductor IC chips and VLSI systems for better safety and security.

Throughout our continuous research and education on the advanced hardware systems at Kobe university, students in the graduate school will gain knowledge of ‘security and safety’ along with ‘analogue and digital’ and experience the practical merge of them in scientific research works and technical developments.

Our academic backgrounds involve the design and evaluation of very large-scale integration (VLSI) systems, the electromagnetic compatibility (EMC), the authenticity and security of hardware devices. Semiconductor solid-state circuits and integrated circuit (IC) chips are always located in the heart of developments. Our alumni contribute to our sustainable society through the innovation of advanced and ubiquitous information and communication technologies. So far, we have more than 80 graduates, including 24 doctoral degree recipients. The laboratory logo of ‘Secafy’ stands for our research activities on hardware security and safety.

Hardware safety and security

Our research targets include the design and development of highly functional cryptographic hardware for securing confidentiality, integrity, availability and authenticity of information data. The demands are continuously growing on information and communication technology (ICT) that can safely and securely manipulate information data with high confidentiality, in the era of internet of things (IoT).

We are challenging exploration toward a comprehensive body of novel technologies of hardware for security. Research topics widely cover the cryptographic engines with high functionality and efficiency, the authenticity of device itself from designs to supply chains, the resiliency against attacks of snooping mainly through side channels, and so forth.

Moreover, our research targets also include the principles of highly reliable electronics hardware, assuring operational safety under harsh environment with diversified disturbances. Hardware systems are generally placed in a variety of physical locations, and as a result suffer from the surrounding environment (specially by electromagnetic (EM) waves that are unseen by humans).

Wireless communication transmitting and receiving large amount of data uses a very subtle EM power. The vehicle to vehicle, as well as to roadside communication units and supporting electronics, and advanced medical and healthcare appliances and supporting electronics, are operating under an dynamically changing environment where hardware-level safety is strongly demanded for robustness, reliability and security.

We are studying hardware safety with particular emphasis on the design principles of electronics with high resiliency for electromagnetic interference (EMI) and electromagnetic susceptibility (EMS), mostly at semiconductor IC chip level.

Research projects

IC chip level noise suppression techniques for high speed and quality wireless communications

Noise suppression techniques were pursued for improving the safety of wireless communication IC chips under undesired interaction with EM disturbance, with special focuses on mobile communication systems using the 2.1 GHz band in long-term evolution (LTE) standards.

The idea was to adopt noise suppression materials, including magnetic components in radio frequency (RF) systems-on-a-chip (SoC) integration. The strategy used behavioural level simulation of wireless communication systems to evaluate the improvement of wireless communication performance by the effect of noise suppression. In addition to this, the undesired noise coupling of RF SoC chips was successfully analysed at the physical level by chip-package-system board (C-P-S) simulation techniques.

These high and low level simulation techniques allow designers to take general looks on the noise coupling problems and to appropriately select the remedies against undesired noise couplings. An on-chip noise monitoring technique originally developed by our group provided in-place noise waveform measurements in an RF SoC chip and assured the sufficient accuracy of the noise coupling simulation for the level of sensitive analogue and RF integrated circuits.

This project had been funded by Ministry of Internal affairs and Communications (MIC), Japan, for Development of Technical Examination Services Concerning Frequency Crowding, in the duration from FY 2010 to FY 2013.

Development of side channel attack sensing techniques and prototyping toward electromagnetic security of cryptographic VLSI circuits

Cryptographic VLSI chips have been pursued for a remarkably high tamper resistance against side channel attacks that have emerged as the non-destructive threats of security vulnerability in cryptographic hardware. The idea was to conversely utilise side channel information leakage as in counter ways for combatting side channel attacks as well as securing the authenticity of devices against counterfeits or even falsification.

The project explored the following three items:

- On-chip detection of the proximate placement and approach of electromagnetic micro probes as the side channel attack sensing technique;

- Integrated simulation techniques of electromagnetic coupling between the electromagnetic micro probe and on-chip side channel sensors and also circuit operations; and

- Positive usage of side channel information for the authentication of cryptographic cores.

The circuits and systems techniques to watch and utilise the side channel leakage will newly establish the methodology of securing devices. A dual-coil side channel sensor disables an attacker with proximate EM probes. The authenticity of an IC chip is supported by its inherent side channel information.

This project was funded by Japan Society for the Promotion of Science (JSPS) for Grants-in-Aid for Scientific Research, KAKENHI, in the duration from FY 2014 to FY 2016.

Noise mitigation techniques against wider frequency of undesired radio waves

The radio environment in general becomes more stringent for the wider data throughput in advanced cellular systems with newly developed electronics systems that potentially emit undesired radio waves, or noises, for wider frequencies. The frequency range of interest for noises from 0.7 to 6 GHz was targeted for:

- Noise measurements; and

- Wireless system level simulation with multiple modes and bands.

The wireless power transfer (WPT) system evolves for the generality of electric and electronic vehicles in our society, whilst emerging as the new source of noises. The developed techniques characterised near-field noises from WPT systems as harmonic components (even with the order higher than 250,000 to the base frequency as low as 85 kHz) and have proven their interference with the communication bands of 2.1 GHz. This comes from the regular occurrence of switching operations of high-speed semiconductor transistors in control unit of the WPT and effectively mitigated by using magnetic component sheets in the internal part of the WPT.

This project had been funded by Ministry of Internal affairs and Communications (MIC), Japan, for Development of Technical Examination Services Concerning Frequency Crowding, in the duration from FY 2015 to FY 2018.

Further research projects have been launched and continued in the area of hardware safety and security, with the comprehensive set of knowledge from IC chip level to system applications.

Biography

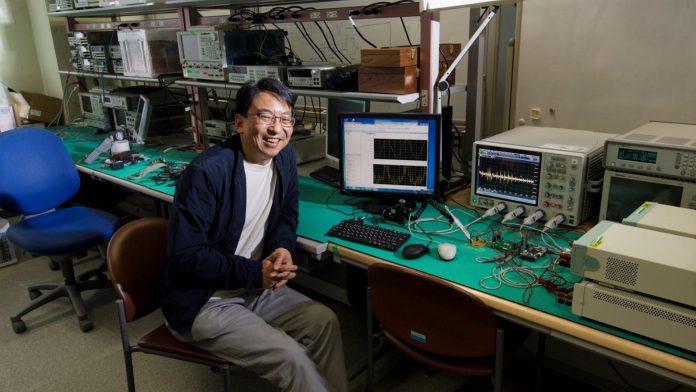

Makoto Nagata received B.S. and M.S. degrees in physics from Gakushuin University, Tokyo, in 1991 and 1993, and a Ph.D. in electronics engineering from Hiroshima University, Hiroshima, in 2001. He was a research associate at Hiroshima University from 1994 to 2002, an associate professor at Kobe University from 2002 to 2009 and promoted to a full professor in 2009. He is currently a professor of the graduate school of science, technology and innovation, Kobe University, Kobe, Japan. He is a senior member of both the IEICE and IEEE.

His research interests include design techniques targeting high-performance mixed analogue, RF and digital VLSI systems with particular emphasis on power/signal/substrate integrity and electromagnetic compatibility, testing and diagnosis, three-dimensional system integration, as well as their applications for hardware security and safety. He was a co-recipient of the best paper awards from IEEE 3D-Test 2013, IACR CHES 2014 and IEEE APEMC 2015.

Makoto Nagata

Professor

Laboratory of hardware security and safety (Secafy)

Graduate School of Science, Technology and Innovation

Kobe University

+81 788036569

nagata@cs.kobe-u.ac.jp