The European Processor Initiative is working to achieve digital sovereignty in high-performance computing by developing European-made processors.

Almost ten years ago, the European Commission decided it needed a special Framework Partnership Agreement (FPA) that would tackle the idea of a European-made processor – if not produced in Europe, then certainly designed and thought of in Europe. Even before creating a special Joint Undertaking, that would synchronise and plot the way for European HPC efforts – the EuroHPC Joint Undertaking – the European Commission included such a plan into the Horizon 2020 programme, the most expansive research and innovation funding programme on the continent.

The European Processor Initiative

A group of industry and research participants formed a consortium, called the European Processor Initiative (EPI), to apply to the topic under the LEIT: ICT work programme. EPI then won the FPA and started off in 2018, under the Specific Grant Agreement 1 (SGA1). The specific challenge of the topic was supporting the creation of a world-class European High-Performance Computing and Big Data ecosystem built on two exascale computing machines, which rank in the first three places in the world. In addition to that, the goal was to “establish, maintain and implement a strategic research and innovation roadmap for building European low-power microprocessor technologies underpinning the build-up of future machines for exascale-class HPC, big data and emerging applications.” Such a processor would help “foster an HPC ecosystem capable of developing new European technology such as low-power HPC chips”.

In a volatile geopolitical situation of the present day, the European plan to work towards digital sovereignty became not only a research and development effort, but a crucial part of the political agenda. According to the conclusions of the European Council from 18 April 2024, ‘the European Council will ensure an integrated approach across all policy areas to increase productivity and sustainable and inclusive growth throughout Europe, build a robust, innovative and resilient economy and advance Europe’s unique social and economic model that will boost the Union’s competitive transition towards digital sovereignty in a self-determined and open manner’.

The first stage (SGA1)

The need to become more independent in all fields, especially digitally, can no longer be viewed as just a strategic idea but a necessity and a priority. The first stage of EPI, the SGA1, thus gathered 28 partners from ten countries, with a strong commitment from both research and industrial sides, to do whatever was in their power and expert capability to deliver this processor and the roadmap for the full length of the EPI.

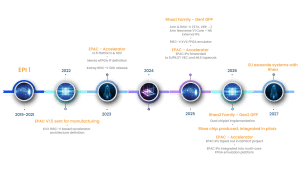

Creating anything from the basic building blocks, let alone a sophisticated and powerful processor, did not come without its hurdles, and the roadmap, of course, had to be adjusted to match all the circumstances, most importantly, the biggest wrench thrown in EPI’s and the world’s plans – the global pandemic. The first stage of EPI ended in 2021, with the road to the two main pillars of EPI clear – Arm family and RISC-V family of processors.

The second stage (SGA2)

The second stage of EPI – EPI SGA2 started off with a kick-off in January 2022, with 30 partners from ten countries, now under the guidance of the formed joint undertaking – EuroHPC JU.

The plan was to continue the development of the outcomes from SGA 1: European microprocessors and accelerators to support European technological autonomy and sovereignty in this critical area.

Innovative developments in high-performance computing

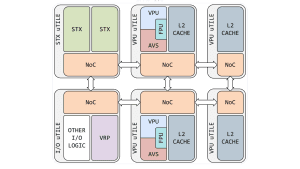

Two main pillars continued from EPI’s plan: an Arm processor family developed by a company incubated within EPI – SiPearl, and a RISC-V-based European processor (EPAC).

In November 2023, the project announced the successful Manufacturing and Silicon Demonstration of its EPAC Accelerator chip version 1.5, marking a significant milestone in high-performance computing.

The successful bring-up of EPAC 1.5 was announced as a major step in the development of the EPI common platform, showcasing the variety of accelerators that can be integrated in future European supercomputers to efficiently address a wide range of computer problems.

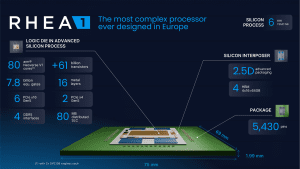

In July 2025, SiPearl, the company incubated within EPI, announced that Rhea1, the most complex processor ever designed in Europe, was sent to tape-out, after SiPearl closed its €130m Series A financing round with a third and last tranche of €32m. It will become available for sampling in early 2026, and according to SiPearl’s announcement, it is supported by a wide range of compilers, libraries and tools, from traditional programming languages such as C/C++, GO and RUST to modern AI frameworks such as TensorFlow and PyTorch. Rhea1 is perfectly suited to traditional HPC workloads – its initial target market – and AI inference workloads.

All these developments were tasked with a specific and concrete goal in mind – one of the missions of EuroHPC JU was to help deploy world-class supercomputers built with European technologies and intellectual property, systems that will ultimately empower European research and development (R&D) and industrial development – and so inclusion of EPI’s IP into European supercomputers targeting exascale became imperative. Upcoming Rhea1 will be included in the JUPITER supercomputer, the fastest supercomputer in Europe. Rhea2, next SiPearl’s processor, was selected to become a part of Alice Recoque – Europe’s newest supercomputer. Alice Recoque will be based in France, and is on track to welcome a scalar compute partition based on the Rhea2 processor developed by SiPearl.

As the project is nearing its completion, an updated roadmap, as a pointer to future developments and outcomes outside of the project, has been announced.

Promising results from consortium partners

Together with the roadmap, the project also announced the beginning of some of the results from partners participating in the consortium: Supercomputing 25, a leading global HPC conference, was the ground to announce two major results from partnering institutions.

Firstly, the French CEA-List, announced the open-source release of VPSim, the Virtual Prototyping Simulator, used for early software-hardware co-validation and performance exploration of the European HPC processor. The institution stated that this will enable the establishment of a community of hardware and software designers dedicated to the European HPC ecosystem, which will accelerate design evaluation while preserving accuracy and software-hardware co-validation phases of next-generation HPC and edge systems.

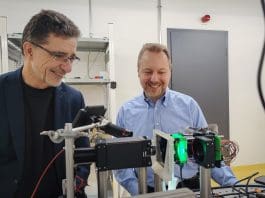

Secondly, Zagreb-based research group announced the creation of Proactive Compute, a new spin-off from University of Zagreb’s Faculty of Electrical Engineering and Computing (UNIZG-FER), and a showcase of two of its key IPs: FAUST and FEVER. FAUST is a high-performance, pipelined floating-point unit (FPU) IP designed for integration into RISC-V cores with vector processing capabilities, while FEVER is a UVM-based RISC-V FPU verification environment that complements FPU design. It is a SystemVerilog DPI wrapper which integrates FEVER into the UVM scoreboard to evaluate the UUT’s outputs.

More such IPs are expected from EPI consortium partners in the upcoming period, as the successful official completion of the project is nearing. In addition to that, research groups from EPI are expected to disseminate final results through various publications and research papers, even though a thorough dissemination repository already lists more than 60 papers, conference proceedings, and book chapters from the duration of the project.

Please Note: This is a Commercial Profile

This work is licensed under Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International.

Please note, this article will also appear in the 25th edition of our quarterly publication.